Le Gate Array

— Basé sur l'article publié dans Quasar CPC numéro 18, Assembleur : Hardware, par OffseT.

— Détailler le fonctionnement des interruptions et la remise à zéro du compteur.

Voici donc un article sur ce fameux Gate Array, le grand gourou électronique du CPC.

Une identité multiple

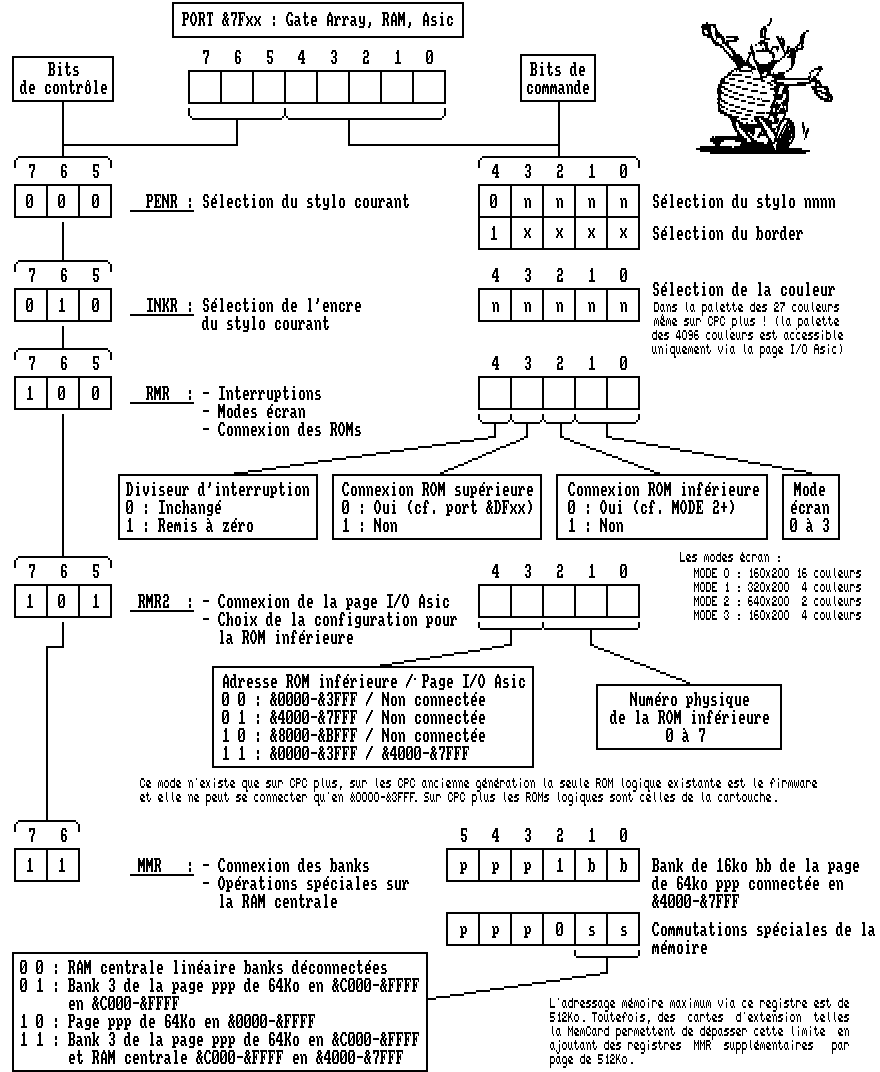

Derrière l'appellation Gate Array, se cachent en fait trois composants essentiels du CPC, tous sur le port

Derrière l'appellation Gate Array, se cachent en fait trois composants essentiels du CPC, tous sur le port &7Fxx :

- le Gate Array proprement dit,

- le PAL 40030 de gestion des banks,

- l'ASIC sur les CPC plus.

Le premier est le circuit qui est réellement au coeur du CPC : il distribue les horloges, génère la vidéo et les interruptions, gère les accès aux ROMs… bref, sans lui pas la peine d'espérer faire fonctionner un CPC. Pratiquement, au niveau logiciel, on va s'adresser à la bête lorsqu'on voudra changer les couleurs et le mode vidéo, retarder les interruptions ou encore modifier l'état des commutations des ROMs. Jetez un coup d'oeil sur le synoptique du port &7Fxx vers la fin de cet article… eh bien notre Gate Array s'occupe des registres PENR, INKR et RMR.

Vient ensuite notre PAL 40030. Physiquement situé juste à côté de notre Gate Array sur la carte mère des CPC6128, celui-ci a pour rôle de gérer nos banks d'extension RAM. C'est lui qui entre en jeu lors de la programmation du registre MMR sur notre port &7Fxx.

Enfin, sur les CPC plus, nous avons l'ASIC. Celui-ci remplace à lui seul les deux chipsets cités ci-dessus en ajoutant par ailleurs le registre RMR2, spécifique à l'adressage des registres de l'ASIC (page I/O ASIC) et aux ROMs du port cartouche.

Cette petite mise au point ayant été faite, nous allons voir de plus près comment réagit ce port. Comme vous le constaterez sur le schéma, l'octet que nous envoyons sur ce port peut être découpé en deux : les trois premiers bits de poids fort (5, 6 et 7) sélectionnent le registre à programmer (PENR, INKR, RMR, etc..)1), et les cinq bits de poids faibles (0 à 4) représentent les paramètres (la valeur associée au registre choisi). Enfin, faites bien attention au fait que ce port fonctionne en écriture seule, impossible d'y lire la moindre information.

Les registres de couleurs

Si vous avez un soupçon d'intuition, vous aurez sans doute compris que ceux-ci sont au nombre de deux : PENR (PENcil Register) et INKR (INK Register). Je ne vais pas m'attarder sur ces deux registres qui sont certainement les plus connus du CPC ! C'est en effet grâce à ces registres qu'il nous est possible de faire des rasters… pour ceux qui ne savent pas comment ça marche, je les renvoie ici.

Si vous avez un soupçon d'intuition, vous aurez sans doute compris que ceux-ci sont au nombre de deux : PENR (PENcil Register) et INKR (INK Register). Je ne vais pas m'attarder sur ces deux registres qui sont certainement les plus connus du CPC ! C'est en effet grâce à ces registres qu'il nous est possible de faire des rasters… pour ceux qui ne savent pas comment ça marche, je les renvoie ici.

En résumé, le registre PENR permet de sélectionner le “crayon” à modifier alors que le registre INKR définit la nouvelle “encre” à affecter au “crayon” courant. Je pense qu'il n'y a pas plus simple ! En outre, il est important de noter que le numéro d'encre (ou de couleur si vous préférez) n'est pas celui communément utilisé sous BASIC (via l'instruction INK), il s'agit en effet des numéros de couleurs dites hardware. À titre de rappel, voici le tableau de correspondance entre les couleurs software (système) et les couleurs hardware (INKR).

|

|

|

Le registre RMR

Nous attaquons les choses sérieuses. Ce registre, RMR (Rom Mapping Register ?), permet de définir de façon cruciale la configuration mémoire et vidéo du CPC. Nous allons donc voir une à une les fonctions qui se cachent dans ses cinq petits bits.

bits 0 et 1 : Sélection du mode graphique

Les deux premiers bits, qui répondent aux doux noms de bit 0 et 1, permettent de choisir le mode vidéo. Ah ! Je vois que le petit blond à lunettes arrive à suivre… ah ben non, il comprend pas : Pourquoi diable y'a-t-il quatre modes possibles (0, 1, 2 ou 3) alors qu'il est bien connu que sur CPC nous n'avons que trois modes graphiques ? hum ? Eh bien la réponse est simple : nous avons effectivement quatre modes vidéo et pas seulement trois ! Ceci étant, le mode supplémentaire (le 3 donc), n'est pas utilisé car il nous offre la résolution du mode 0 avec le nombre de couleurs du mode 1 ! Autant dire qu'on peut facilement s'en passer !

bit 2 : Activation de la ROM inférieure

Le bit qui suit (oui, c'est bien le bit 2, un bon point pour le petit blond à lunettes qui a su rester concentré) nous permet de commander la connexion de la ROM inférieure. Mais qu'est-ce donc que la ROM inférieure ? Sur CPC ancienne génération, rien de plus simple, il s'agit de la ROM Firmware, celle qui contient le système d'exploitation du CPC ; attention, ce n'est pas la ROM BASIC ! Cette ROM se connecte sur la page mémoire &0000-&3FFF. Sur CPC+, c'est un peu plus complexe puisque l'adresse et le contenu de la ROM inférieure sont déterminées via le registre RMR2 décrit un peu plus loin.

bit 3 : Activation de la ROM supérieure

Vient ensuite le bit 3. Celui-ci nous permet de commuter la ROM supérieure. Le petit blond à lunettes est complètement largué… j'explique : cette fameuse ROM se connecte en &C000-&FFFF et peut être n'importe quelle ROM d'extension de votre CPC. Sur un CPC6128 de base, nous n'avons que deux ROMs d'extension :

- la ROM 0 (qui contient le BASIC),

- la ROM 7 (qui contient l'Amsdos).

Mais il est possible d'en ajouter presque à volonté (256 ROMs au maximum) grâce à des extensions telles que le Romboard, la Romcard ou la Ramcard2).

Le choix du numéro de la ROM commutée se fait grâce à un registre auxiliaire situé sur le port &DFxx. Ce port est détaillé ci-après. Vous pouvez constater que s'il est très simple sur les CPC ancienne génération (on y envoie le numéro de la ROM que l'on désire commuter), il dispose de deux modes de fonctionnement sur CPC+. Lorsque le bit 7 vaut 0 (valeurs 0 à 127), il se comporte comme sur les vieux CPC et représente le numéro de ROM à commuter3). En revanche, quand ce bit 7 est mis à 1, les bits 0 à 4 permettent alors de choisir le numéro de ROM de la cartouche à commuter !4)) Eh oui, sur CPC+, outre les ROMs d'extension classiques, nous avons des cartouches qui ne sont ni plus ni moins que d'autres ROMs d'extension.

Afin d'éviter tout confusion, les ROMs d'extension classique (comme sur CPC ancienne génération) s'appellent les ROMs logiques ; et les ROMs d'extension contenues dans les cartouches des CPC+, les ROMs physiques.

Port

Port &DFxx sur CPC ancienne génération :

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| n | n | n | n | n | n | n | n |

- nnnnnnnn : numéro de ROM logique (0-255).

Port &DFxx sur CPC plus :

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | n | n | n | n | n | n | n |

| 1 | x | x | p | p | p | p | p |

- nnnnnnn : numéro de ROM logique (0-127).

- ppppp : numéro de ROM physique (0-31).

- xx : non utilisé.

Sur un CPC de base5), les ROMs logiques6) disponibles sont :

- ROM 0 : BASIC,

- ROM 7 : Amsdos (sauf sur CPC464).

Sur un CPC+7), les ROM physiques8) disponibles sont :

- ROM 0 : Firmware,

- ROM 1 : BASIC,

- ROM 2 : Vierge (inutilisée),

- ROM 3 : Amsdos,

- ROM 4 : Burnin' Rubber ROM 0,

- ROM 5 : Burnin' Rubber ROM 1,

- ROM 6 : Burnin' Rubber ROM 2,

- ROM 7 : Burnin' Rubber ROM 3.

Nooooon ! J'y crois pas, le petit blond à lunettes a une forme d'enfer aujourd'hui ! Il a remarqué une petite subtilité intéressante. Sur CPC+, si une ROM ne peut être accessible que par un numéro physique ou un numéro logique, il existe des ROMs qui sont accessibles via les deux normes ! Eh oui, la ROM BASIC par exemple, porte le numéro logique 0 et le numéro physique 1 ; mais c'est également le cas de la ROM Amsdos qui a le numéro physique 3 et logique 7. Ceci dit, si le numéro physique est une constante (d'où son nom), la ROM correspondant à un numéro logique peut-être changée. En effet, si, sur CPC+, vous connectez une Ramcard dans laquelle vous programmez la ROM Parados en numéro 7, eh bien la ROM logique numéro 7 sera désormais Parados mais la ROM physique 2 (qui était aussi la ROM logique 7) reste l'Amsdos !9)

bit 4 : Retard d'interruption

Pour en finir avec ce registre, nous avons le petit bit 4. Si vous le mettez à zéro rien ne se passe. En revanche, lorsque vous le mettez à 1, vous faites une remise à zéro du diviseur d'interruption. Mais qu'est-ce donc que cette bestiole ? Eh bien, comme vous le savez certainement, le Gate Array gènère les interruptions dans le CPC : c'est lui qui, tous les 300èmes de secondes (ou toutes les 52 lignes de HBL si vous préférez) demande à notre Z80 d'entrer en interruption10). Lorsque vous mettez le diviseur à zéro (ce qui a lieu automatiquement à chaque VBL et toutes les 52 HBL) vous allez retarder la prochaine interruption en provenance du Gate Array ; elle aura lieu 52 lignes plus bas (à partir de votre remise à zéro).

Pour en finir avec ce registre, nous avons le petit bit 4. Si vous le mettez à zéro rien ne se passe. En revanche, lorsque vous le mettez à 1, vous faites une remise à zéro du diviseur d'interruption. Mais qu'est-ce donc que cette bestiole ? Eh bien, comme vous le savez certainement, le Gate Array gènère les interruptions dans le CPC : c'est lui qui, tous les 300èmes de secondes (ou toutes les 52 lignes de HBL si vous préférez) demande à notre Z80 d'entrer en interruption10). Lorsque vous mettez le diviseur à zéro (ce qui a lieu automatiquement à chaque VBL et toutes les 52 HBL) vous allez retarder la prochaine interruption en provenance du Gate Array ; elle aura lieu 52 lignes plus bas (à partir de votre remise à zéro).

Le registre RMR2

Ce registre est disponible uniquement sur CPC+. Il a deux objectifs : connecter/déconnecter la page I/O des registres de l'ASIC et configurer la ROM inférieure (dont la connexion est pilotée via le bit 2 du registre RMR). Les trois bits inférieurs nous permettent de choisir le numéro de la ROM physique (parmi les huit premières) qui sera commutée en tant que ROM inférieure. Les deux bits suivants sélectionnent la configuration ROM/ASIC désirée. On peut choisir de commuter la ROM inférieure en &0000-&3FFF, &4000-&7FFF ou &8000-&BFFF. Une combinaison permet également de commuter la page I/O ASIC en &4000-&7FFF ; dans ce cas précis la ROM basse se trouve alors en &0000-&3FFF.

Par défaut, le registre RMR2 vaut 0 ce qui signifie que la page I/O ASIC est déconnectée, la ROM inférieure commutable en &0000-&3FFF, et qu'il s'agit de la ROM physique numéro 0. Nous sommes dans ce cas entièrement compatible avec l'adressage de la ROM inférieure des CPC ancienne génération puisqu'il se trouve que la ROM physique 0 de la cartouche système des CPC+ est le firmware (pfiou, on a eu chaud !).

Le dernier : le registre MMR

Ce registre (Memory Mapping Register ?) comme son nom l'indique, est dédié à la gestion de la mémoire du CPC. Il permet de choisir la page de 64ko dans laquelle sélectionner la bank de 16ko à commuter en &4000-&7FFF. Il offre également la possibilité d'effectuer des commutations de RAM spéciales qui sont décrites sur le schéma qui suit. Je vous rappelle juste que sur CPC464 ou CPC664, il n'y a pas de RAM d'extention et que sur CPC6128 il y a une page de 64ko (la numéro 1) d'extension.

Ce registre permet en théorie un adressage maximum de 512ko. On peut toutefois passer outre grâce à des registres MMR auxilaires comme cela est le cas dans la fameuse Memcard 2Mo de Ram7. Cette carte, en plus du registre MMR qui permet l'accès aux 512 premiers kilo-octets, offre 3 autres registres similaires sur d'autres ports : en fait nous avons un registre MMR par page de 512ko.

Quelques détails

Je pense que nous avons à peu près fait le tour des fonctions accessibles via le port &7Fxx. Je vous propose maintenant de mettre en avant quelques variantes dans le fonctionnement du Gate Array émulé par l'ASIC des CPC+.

Tout d'abord, en ce qui concerne la mise à jour des couleurs par rapport aux données vidéo, vous constaterez, si vous vous essayez aux split-rasters, que sur CPC+11) ceux-ci sont décalés d'une microseconde12) vers la droite. Donc, si vous avez à mettre en place des split-rasters avec un positionnement bien précis par rapport à ce qui est affiché à l'écran, pensez à en tenir compte !

Ensuite, concernant la programmation des registres PENR et INKR sur CPC+, étant donné que celui-ci dispose d'une palette de 4096 couleurs (RVB 12 bits) au lieu de 27 couleurs, vous devez bien comprendre que l'ASIC fait en fait une conversion du codage de couleurs “ancienne génération” vers son propre code RVB. La palette des 27 couleurs des CPC classiques est déduite d'un codage RVB trois états, chaque composant RVB pouvant être à zéro, à demi-intensité, ou à pleine intensité. En revanche, sur CPC+, le codage RVB est du 4 bits (valeurs de 0 à 15) pour chacun de ces mêmes composantes. Ah ! Je vois que le petit blond à lunettes a compris le problème ! Décidément, il devient bon ! Lors de la conversion, la pleine intensité c'est évidemment 15… et la demi-intensité ? Hum… 15/2=7,5… On met quoi alors ? 7 ou bien 8 ? Eh bien l'ASIC met 6 ! Mais pourquoi 6 ? L'astuce vient du fait que la “demi-intensité” du CPC n'est en fait pas demi du tout. Le niveau haut ne vaut pas le double du demi-niveau d'intensité, c'est pourquoi la palette du CPC contient des couleurs très proches : l'échelle n'est pas linéaire. Ceci dit, malgré cette conversion à 6 plutôt que 7 voire 8, les couleurs “ancienne génération” apparaissent toujours plus vives sur un CPC+ que sur un CPC… mais bon, si vous essayez de convertir à la main à 5 plutôt que 6, vous constaterez que vous êtes trop pâles… la bonne valeur serait effectivement entre les deux.

Quelques informations sur les ports

Je vous propose un petit jeu amusant. Depuis notre bon vieux BASIC, tapez la liste suivante :

Je vous propose un petit jeu amusant. Depuis notre bon vieux BASIC, tapez la liste suivante :

OUT &7F00,&10:OUT &7F00,&40

Vous avez logiquement un flash gris (couleurs hardware INKR=0) dans le border (PENR=&10)… Je vous rappelle en effet que le système d'exploitation remet les couleurs à jour régulièrement, donc votre modification ne dure pas. Mais bon, le sujet n'est pas là ; tapez maintenant :

OUT 0,&C2

Paf, votre CPC a planté ! C'est normal, vous avez activé le mode spécial du registre MMR qui consiste à échanger les 64ko de base avec les premiers 64ko d'extension : crash inévitable… pourtant… comment se fait-il que le registre MMR ait été programmé puisqu'on n'a pas accédé au bon port ?

De plus, tapez le premier exemple mais sur le port 0 au lieu du port &7F00 :

OUT 0,&10:OUT 0,&40

Ça ne marche pas ! Aucun changement de couleurs au rendez-vous ! En fait, tout ceci est normal.

Rappelez-vous, le registre MMR est pris en compte par le PAL et non par le Gate Array ! Or il se trouve que le Gate Array réagit à tous les ports pour lesquels le bit 15 est à zéro et le bit 14 à un, alors que le PAL se contente du bit 15 à zéro… pensez-y lorsque vous optimiserez vos accès via les ports &xC00 et &xDxx plutôt que &BCxx et &BDxx ; le PAL vous guette !

Pour information, voici un petit tableau illustrant le décodage physique des ports I/O par le CPC :

| Nom des périphériques | bits décodés par le CPC | |||||||

|---|---|---|---|---|---|---|---|---|

| (adresse des ports logiques) | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

Gate Array - PENR, INKR (&7Fxx) | 0 | 1 | x | x | x | x | x | x |

Gate Array - RMR, MMR (&7Fxx) | 0 | x | x | x | x | x | x | x |

CRTC (&BCxx-&BFxx) | x | 0 | x | x | x | x | r | r |

Sélection ROM Haute (&DFxx) | x | x | 0 | x | x | x | x | x |

Imprimante (&EFxx) | x | x | x | 0 | x | x | x | x |

PPI (&F4xx-&F7xx) | x | x | x | x | 0 | x | r | r |

| Périphériques d'expansion | x | x | x | x | x | 0 | r | r |

À présent, prenez un CPC et un CPC+ et comparez ce que fait la ligne suivante sur chacun de ces ordinateurs :

OUT &7F00,&10:a=INP(&7F00)

Intéressant non ? Je vous laisse deviner ce qui se passe13).

Le schéma général du Gate Array

— Directement extrait de Quasar CPC numéro 19, à rectifier et à refaire dans une meilleure résolution.

Documentations externes

- La génération des couleurs par le Gate Array sur le site du groupe Shinra.

- Documentation technique détaillée du Gate Array sur Grimware.org (anglais).